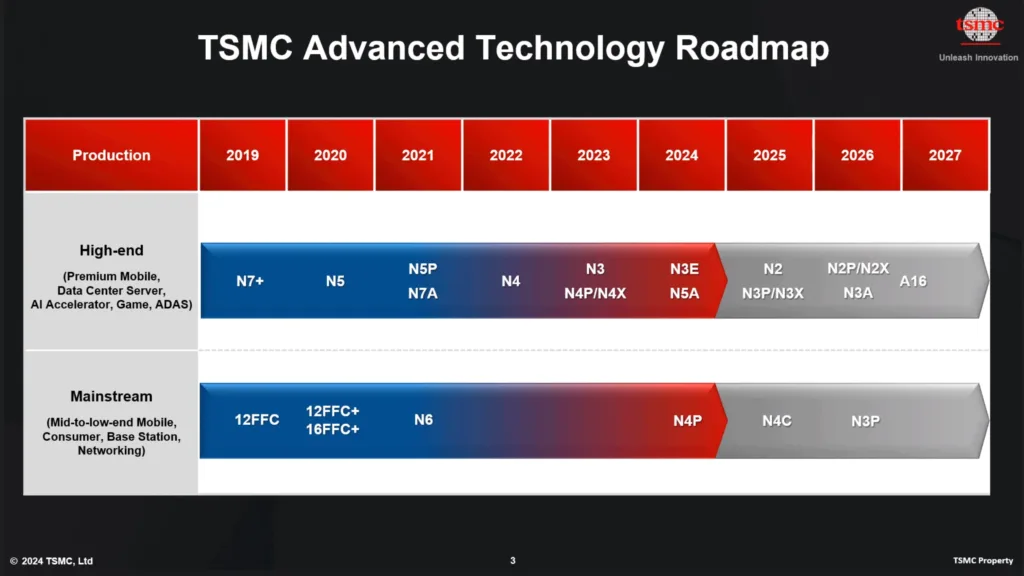

As we enter 2025, the semiconductor industry TSMC stands on the brink of another technological milestone with its N2 process node. Last year, at TSMC’s North American Technology Symposium 2024, the semiconductor manufacturing giant revealed crucial updates about its upcoming (N2 ~2nm) process node. While the core timeline (as shared by TSMC during N3 node reveal) more or less remains unchanged.

Following the successful implementation of the N3 family, which brought the innovative FinFlex technology to market, TSMC’s N2 node represents the company’s next major advancement in semiconductor manufacturing. The announcement and subsequent updates throughout 2024 have revealed several developments about N2 node.

While commonly referred to as “2 nanometer” technology, it’s important to understand that modern node naming conventions like “N2” represent a general class of manufacturing processes rather than exact physical measurements. These names primarily serve as marketing terms indicating generational improvements over previous nodes, as the actual transistor dimensions vary across different chip components and manufacturers.

Key Takeaways

- Mass Production Timeline: TSMC’s first-generation N2 node enters risk production in early 2025 and high-volume manufacturing (HVM) by late 2025—on track for consumer devices by late 2026.

- Performance Gains: Compared to its N3E (enhanced 3nm) process:

- 10–15% faster speeds at identical power

- 25–30% lower power consumption at matched clocks

- ~15% logic density improvement

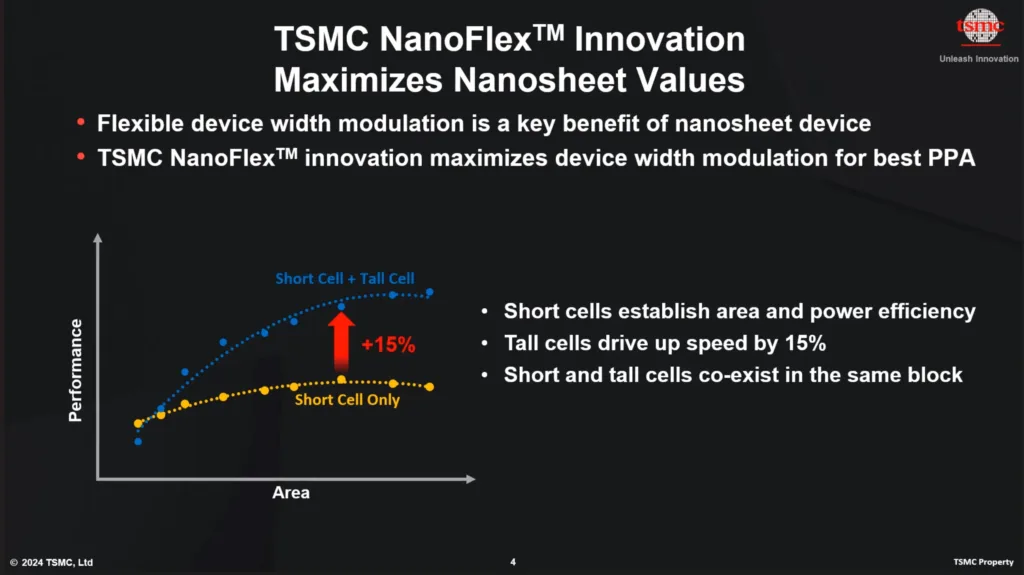

- NanoFlex replaces FinFlex: A GAAFET-driven upgrade allowing designers to mix-and-match cell libraries within blocks (e.g., tall cells for speed + short cells for efficiency).

- Backside Power Delay: Previously planned for N2P (performance-enhanced variant), BSPDN (backside power delivery) is deferred until post-N2 nodes due to cost/complexity concerns.

N2 Production Timeline and Positioning

TSMC has successfully maintained its commitment to begin risk production of N2 in early 2025, followed by volume production in the second half of 2025.

This timeline suggests we’ll see the first consumer devices featuring N2 chips in early 2026.

The extended development cycle between nodes reflects the increasing complexity of semiconductor manufacturing at such microscopic scales – a trend we previously observed with the N3 family’s implementation.

Even-though, the recent reports from supply chain sources indicate that while TSMC has achieved better-than-expected production yield rates exceeding 60% in early testing. But, the company still needs to work more improving these numbers to meet mass production requirements.

This complexity is further evidenced by TSMC’s strategic pricing decisions and ongoing efforts to scale production capacity to meet what Chairman Mark Liu has described as “unexpectedly high customer demand.”

The technical and high demand challenges of N2 production are reflected in its manufacturing costs, with wafer prices reportedly set significantly higher than previous nodes, highlighting the increasing complexity and precision required for these advanced manufacturing processes.

This has already impacted customer timelines – notably leading Apple to reportedly postpone its N2 chip adoption to 2026, delaying its initial plans for the iPhone 17 series.

Other major players like NVIDIA and Qualcomm are also reportedly reevaluating their N2 manufacturing strategies and thinking to shift to Samsung foundry, in light of these early production metrics.

Comparison of TSMC N2 node with TSMC N3 node

When compared to the current N3E node, N2 promises significant improvements:

- Performance boost of 10-15% at identical power consumption levels

- Power reduction of 25-30% while maintaining the same frequency and complexity

- Logic density increase of 15%, marking substantial progress in transistor scaling

The GAAFET Revolution

N2 represents TSMC’s first implementation of gate-all-around (GAAFET) nanosheet transistors, marking a departure from the FinFET architecture used in N3 and earlier nodes. While the FinFET-based FinFlex technology served as a powerful innovation for N3, the transition to GAAFET architecture opens new possibilities for transistor design and optimization.

For its upcoming N2 node, however, TSMC transitions entirely to nanosheet-based GAAFET (gate-all-around field-effect transistors)—a shift rivaled only by Intel’s RibbonFET (20A/18A) and Samsung’s SF² plans.

The GAAFET architecture completely surrounds the channel with gate material, offering superior electrostatic control compared to FinFET designs. This architectural shift enables better performance at lower power consumption levels, crucial for maintaining Moore’s Law progression.

Samsung has also introduced the multi-bridge field effect transistor (MBCFET) architecture surrounding the gate transistor (GAAFET) for its 2nm chip, but so far the production has not been ramped up, and efforts are being made to improve the MBCFET process. On the other hand Intel 18A (~1.8 nm) will introduce ribbon field effect transistors (RibbonFET) based on GAAFET. In addition Japan’s Rapidus is also striving for 2nm chip production by 2027.

NanoFlex Technology: Advanced Cell Design Flexibility

TSMC’s journey toward smaller nodes took a pivotal turn at 3nm with FinFlex, which let chipmakers blend transistor configurations (e.g., ultra-dense “1-fin” vs high-speed “3-fin” cells) on the same die using FinFET architecture.

Building upon the success of FinFlex in the N3 node, TSMC’s new NanoFlex technology leverages the unique capabilities of GAAFET architecture. NanoFlex will be implemented across the entire N2 family, including N2, N2P, and N2X variants.

What Makes NanoFlex Special?

The technology offers great control over cell design through multiple optimization paths:

- Channel Width Optimization:

- Allows fine-tuning of transistor characteristics

- Enables precise balance between performance and power consumption

- Supports customization at the cell level

- Cell Height Variations:

- Short cells: Optimized for area efficiency and power conservation

- Tall cells: Deliver up to 15% higher performance

- Mixed implementation possible within the same block design

- Library Integration:

- Seamless mixing of cells from different libraries

- High-performance cells can coexist with low-power variants

- Area-efficient cells can be implemented where density is crucial

Power Delivery Innovations

A significant update to TSMC’s N2 roadmap involves power delivery architecture. While the initially planned backside power delivery network (BSPDN) for N2P has been postponed, TSMC has introduced super-high-performance metal-insulator-metal (SHPMIM) capacitors.

SHPMIM Capacitor Advantages:

- More than 100% increase in capacity density compared to previous SHDMIM capacitors

- 50% reduction in sheet resistance (Rs in Ohm/square)

- 50% lower via resistance (Rc)

- Enhanced power supply stability for complex chip designs

N2 Process Family Expansion

TSMC’s N2 will develop into a comprehensive family of process nodes:

- N2 (2025 H2?):

- First-generation GAAFET implementation

- Baseline performance and efficiency improvements

- SHPMIM capacitor integration

- N2P (2026):

- Performance-enhanced variant

- Further optimized for high-performance computing

- Originally planned BSPDN feature moved to future nodes

- N2X (2026):

- Voltage-enhanced version

- Targeted at high-performance computing and AI applications

- Optimized for sustained high-power operation

All variants will support NanoFlex technology, ensuring design flexibility across the entire N2 family. This approach mirrors the successful strategy employed with the N3 node family, where different variants catered to specific use cases and market segments.

Looking Back and Forward: N3 to N2 Transition

The transition from N3 to N2 represents a more significant technological leap than previous node transitions, primarily due to the shift from FinFET to GAAFET architecture. While N3’s FinFlex technology revolutionized design flexibility within the FinFET paradigm, NanoFlex takes this concept further by leveraging GAAFET’s inherent advantages.

This evolution in manufacturing technology will enable:

- More sophisticated chip designs

- Better performance/power optimization

- Enhanced flexibility in meeting diverse application requirements

- Continued scaling of semiconductor technology

Market Impact and Applications

The N2 node’s capabilities will be particularly crucial for:

- Next-generation mobile processors

- High-performance computing chips

- AI and machine learning accelerators

- Advanced networking and telecommunications equipment

Early adopters, likely including major players like Apple, will benefit from the node’s improved performance and efficiency characteristics, though at a premium similar to early N3 adoption.

TSMC along with Samsung Foundry, Intel and Japans Rapidus, the semiconductor manufacturers have officially launched a GAAFET architecture competition. But, looking at current state of affairs and previous record, most of the industry believes that TSMC will continue to lead in the 2-nm process.

Leave a Reply

You must be logged in to post a comment.