Phoronix first reported this in the recent Linux fixes. Intel has already confirmed the use of Level 4 caches in their future Meteor Lake System on a Chip. Other than confirming the return of the L4 cache on processors, Meteor Lake implementation details are lacking.

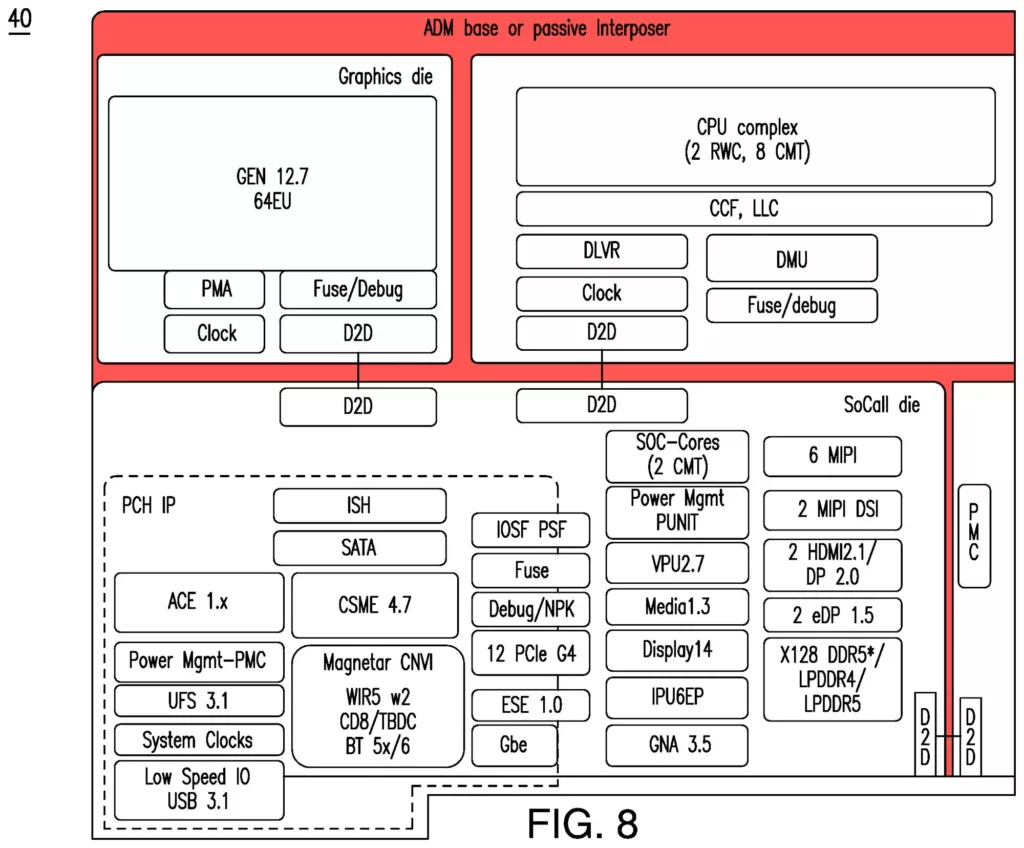

According to a recent source, “Meteor Lake” introduces an L4 cache, which is dubbed “Adamantine” and fulfills functions similar to that of a passive interposer. Intel’s planned “Meteor Lake” microarchitecture will power the company’s first client-side disaggregated CPU.

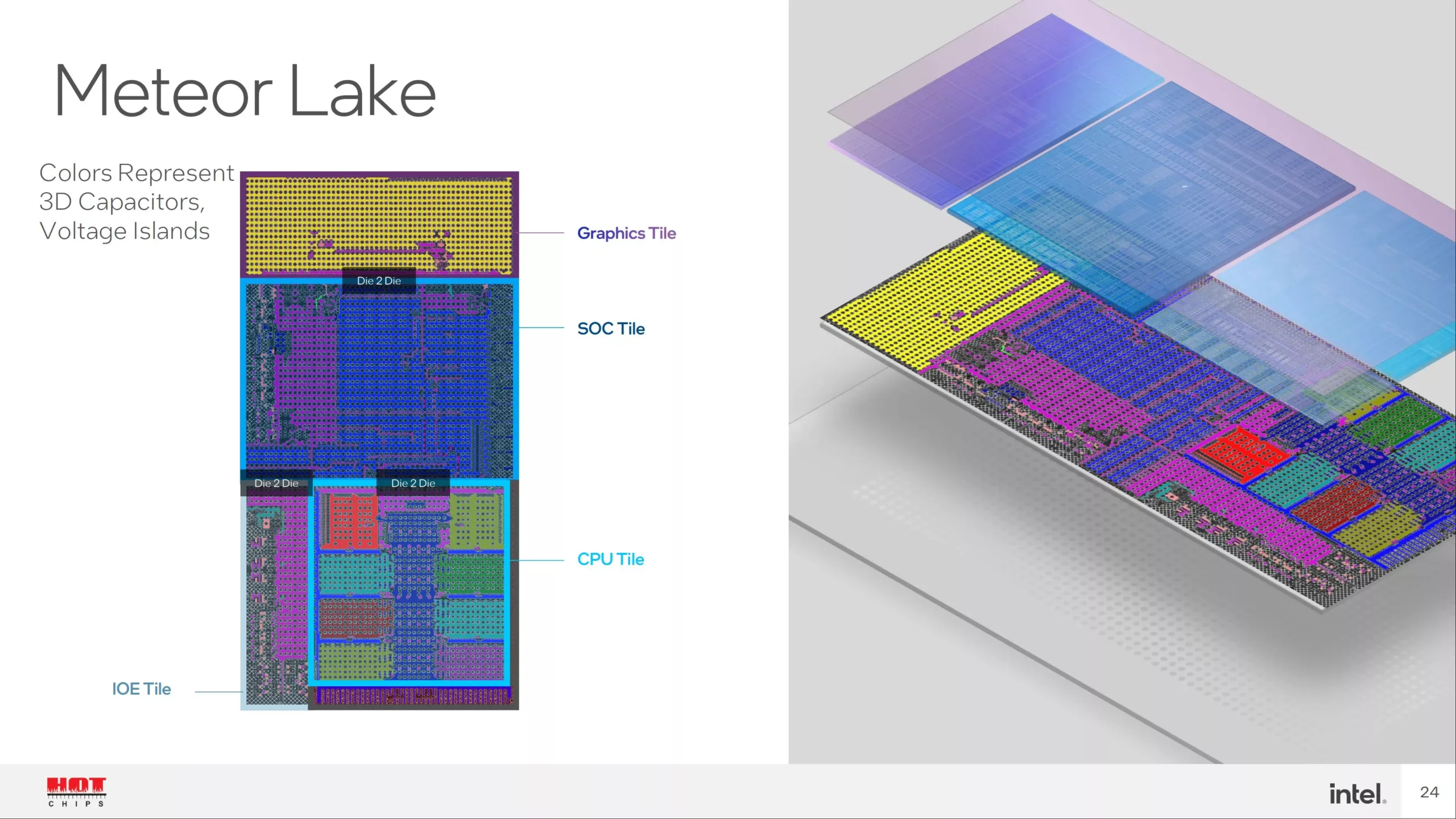

A disaggregated processor differs from an MCM (such as “Clarkdale”) in that finer component that make up the processor that would otherwise be too late to exist on their own packages are made to share a single package via a high-speed link.

This disaggregation is done solely for economic reasons, as Intel does not need to use the most recent (and most expensive) foundry node for the entire processor, but rather ration it to the precise components that benefit the most from it.

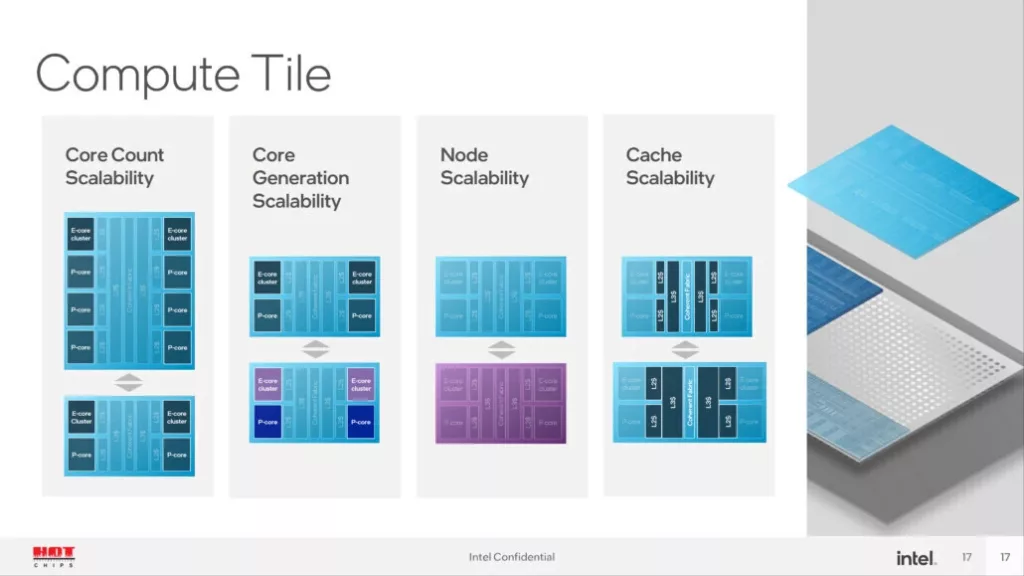

Cache implementation

Modern processors often use L1, L2, and L3 caches, with the L1 version being the quickest and smallest and the others being larger but slower. L4 caches are frequently superfluous since they use a large amount of space on the processor die while providing little benefit, causing manufacturing costs to skyrocket.

However, given Meteor Lake’s multi-die tile architecture, we’re curious where the L4 cache will wind up. We saw integration into the foundation tile, which houses the computing cores and other critical compute elements. This makes the most sense because the logic requires fast memory access, and L4 could boost speed in specific situations.

Also read: Check the performance and benchmarks for Intel i5-13500

Meteor Lake will completely embrace the hybrid architecture, which will combine five separate tiles: CPU, SoC, GPU, I/O, and the base tile. The Adamantine cache would provide significantly faster access than any other cache, such as L3, which is normally part of the CPU tile.

The major function of the L4 cache, according to Intel, is to improve boot optimisation and boost security around the host CPU. Furthermore, the L4 cache would retain the cache during reset, resulting in faster loading speeds that would otherwise need all boot/reset cycles.

The patent is coupled to a block schematic that clearly shows a Meteor Lake with two RWC (Redwood Cove) cores and eight CMT (Crestmont) cores. Interestingly, the SOC tile also shows two CMT cores, which were previously discussed in leaks. This design would also include Gen 12.7 Xe graphics with 64 EUs.

Moore’s Law is Dead also highlighted the Adamantine cache in his last video, claiming that the cache might expand into ‘gigabytes,’ but it is currently tested in capacities ranging from 128MB to 512MB.

Officially, Intel Meteor Lake will be available in the second half of 2023.

Leave a Reply

You must be logged in to post a comment.